# Characterization of Interface Trap Density of In-rich InGaAs nMOSFETs with ALD Al<sub>2</sub>O<sub>3</sub> as Gate Dielectric

Saima Sharmin, Urmita Sikder, Rifat-Ul-Ferdous and Quazi D. M. Khosru

Abstract—In this paper, we characterize the interface properties of In-rich  $In_{0.65}Ga_{0.35}As$  and  $In_{0.75}Ga_{0.25}As$ MOSFETs with ALD  $Al_2O_3$  gate dielectric. Interface trap density is extracted from physically based quantum mechanical low frequency CV model. We show that donor-like traps dominate the D<sub>it</sub> profile for  $In_{0.75}Ga_{0.25}As$ -channel compared to  $In_{0.65}Ga_{0.35}As$ -channel MOSFETs. This result explains the reason of stronger inversion of In-rich surface channel MOSFETs and hence, better transport characteristics in spite of high interface trap density.

# I. INTRODUCTION

THE continuous scaling of MOS transistors has brought the feature size into nanometer regime and pushed the Si CMOS technology into its fundamental limits. According to ITRS 2009 edition, scaling of the equivalent oxide thickness (EOT) of gate dielectrics below 0.6 nm for 16nm node is the toughest challenge before further device scaling [1]. High- $\kappa$  gate dielectrics are known to circumvent the problems of excessive gate tunneling current and other reliability problems while alternative materials like high mobility III-V compound semiconductors are considered for the replacement of Si in device technology. Integrating high-mobility channels with high- $\kappa$  dielectric has recently emerged as a leading candidate for next-generation technology on and beyond 16nm node [1].

However, the challenge introduced by the poor interface properties of high-k dielectrics with III-V materials is yet to be overcome. The effect of interface properties on transport characteristics depends on interface trap types (donor- or acceptor-like) as well as trap density. So the correct extraction of interface trap density is important for characterizing the high- $\kappa$ /III-V interface. In<sub>x</sub>Ga<sub>1-x</sub>As compound semiconductor is attractive as a channel material due to its high bulk electron mobility. A lot of research effort is centered on understanding the properties of In<sub>x</sub>Ga<sub>1-x</sub>As MOSFET with ALD Al<sub>2</sub>O<sub>3</sub> gate dielectric [2]-[7].

Manuscript received June 15, 2010.

Saima Sharmin, Urmita Sikder and Rifat-Ul-Ferdous are undergraduate students of the Department of Electrical and Electronic Engineering in Bangladesh University of Engineering and Technology, Bangladesh. (e-mail: sharmin.saima@yahoo.com).

Quazi D. M. Khosru is with the Department of Electrical and Electronic Engineering in Bangladesh University of Engineering and Technology, Bangladesh. (e-mail: qdmkhosru@eee.buet.ac.bd).

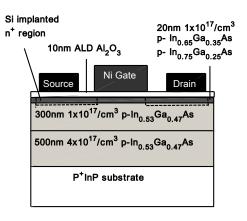

In this work, we used a modified physically based QM CV model for simulating an enhancement type InGaAs heterostructure nMOSFET with In-rich surface channel and ALD  $Al_2O_3$  as gate dielectric. A schematic cross-sectional view of the MOSFET used in this study is shown in Fig.1.

Fig. 1. Schematic cross-sectional diagram of surface channel InGaAs nMOSFET used in the study

The ideal CV characteristics obtained from this model is used to extract the interface trap density from experimental low frequency CV characteristics [5], [6] of both  $In_{0.75}Ga_{0.25}As$  and  $In_{0.65}Ga_{0.35}As$  nMOSFETs to study the effect of changing the percentage of channel In-content on the interface properties. The extracted interface trap density profiles are also compared with experimental profiles obtained from HF-LF method [5], [6].

## II. MODELING

In our CV model, quantized electronic states of MOS inversion/accumulation are calculated via self-consistent solution of coupled 1-D Schrödinger's and Poisson's equations within the effective mass approximation [8]. 1-D Schrödinger's equation is solved by Hamiltonian matrix formalism based on finite difference method [9]. The effect of wave function penetration is considered using finite barrier height at oxide-semiconductor interface. Carriers in the three-dimensional (3-D) extended states under accumulation bias are taken into account semiclassically using Fermi-Dirac statistics and parabolic density of states [10]. Poisson's equation is solved using finite difference method with uniform meshing.

The effect of biaxial compressive strain on the channel layer is incorporated in our adapted model by considering the shifting of conduction and valence band edges along with the change of effective masses. The strain splits the valence band at the zone centre and shifts the spin-orbit band. The degenerated HH and LH bands split into higher HH and lower LH respectively. This shifting results in an increase in the effective bandgap. The amount of shifting is calculated using the following formulas [11]:

$$E_{hh}(0) = E_v^0 - P_\varepsilon - Q_\varepsilon \tag{1}$$

$$E_{lh}(0) = E_{\nu}^{0} - P_{\varepsilon} + \frac{1}{2} \left[ Q_{\varepsilon} - \Delta_{0} + \sqrt{\Delta_{0}^{2} + 9Q_{\varepsilon}^{2} + 2Q_{\varepsilon}\Delta_{0}} \right]$$

(2)

$$E_{so}(0) = E_v^0 - P_\varepsilon + \frac{1}{2} \left[ Q_\varepsilon - \Delta_0 - \sqrt{\Delta_0^2 + 9Q_\varepsilon^2 + 2Q_\varepsilon \Delta_0} \right]$$

(3)

$$E_{c}(0) = E_{v}(0) + E_{g} + a_{c}(\varepsilon_{xx} + \varepsilon_{yy} + \varepsilon_{zz})$$

$$(4)$$

$$P_{\varepsilon} = -a_{v} (\varepsilon_{xx} + \varepsilon_{yy} + \varepsilon_{zz})$$

$$(5)$$

$$Q_{\varepsilon} = -\frac{b}{2} \left( \varepsilon_{xx} + \varepsilon_{yy} - 2\varepsilon_{zz} \right) \tag{6}$$

Here  $\varepsilon_{zz}$  is the relative change of lattice period in the perpendicular direction and  $\varepsilon_{xx}$  and  $\varepsilon_{yy}$  are the relative change in lattice period in the in-plane direction.  $\Delta_0$  is the split-off energy. Factors  $a_c$  and  $a_v$  are hydrostatic deformation potentials; while b is the shear deformation potential.

Biaxial compressive strain causes the curvatures of the energy band structures and consequently effective masses to change. The hole effective masses of the channel and substrate are calculated using the well known Luttinger parameters  $\gamma_1$ ,  $\gamma_2$  and  $\gamma_3$  for k=0 [11].

|                  | TABLE I                        |                               |

|------------------|--------------------------------|-------------------------------|

|                  | HOLE EFFECTIVE MAS             | S                             |

|                  | NORMAL MASS                    | DOS-MASS                      |

|                  | $(m_z / m_0)$                  | $(m_{d}/m_{0})$               |

| $HH(m_{hh}/m_0)$ | $1/(\gamma_1 - 2\gamma_2)$     | $1/(\gamma_1 + \gamma_2)$     |

| $LH(m_{lh}/m_0)$ | $1/(\gamma_1 + 2\gamma_2 f_+)$ | $1/(\gamma_1 - \gamma_2 f_+)$ |

| $SO(m_{so}/m_0)$ | $1/(\gamma_1 + 2\gamma_2 f)$   | $1/(\gamma_1 - \gamma_2 f)$   |

Here  $f_{\pm}$  is the strain factor calculated from the strain parameter,  $s=Q_{\epsilon}/\Delta_0$ .

# III. D<sub>IT</sub> EXTRACTION

The density of interface trap states for the mentioned device is extracted using the technique proposed by Satter and Haque [12], [13]. Parallel capacitance,  $C_p$  and semiconductor capacitance,  $C_s$  are extracted from experimental quasistatic C-V [5], [6] and ideal gate CV respectively. Experimental gate capacitance,  $C_{ox}$  and  $C_p$ ; while simulated ideal  $C_g$  with zero  $D_{it}$  is the series combination of semiconductor capacitance,  $C_s$  and  $C_{ox}$ . Correct extraction of dielectric capacitance is necessary for both  $C_p$  and  $C_s$

calculation. Correct  $C_{ox}$  is extracted from experimental accumulation gate CV using the technique of Islam and Haque [10].

For depletion and inversion region,  $C_p$  is the parallel combination of depletion capacitance,  $C_{depl}$ , inversion capacitance,  $C_{inv}$  and interface trap capacitance,  $C_{it}$ , whereas  $C_p = C_{acc} + C_{it}$  for accumulation bias. In other words,  $C_p$  is the parallel combination of  $C_s$  (= $C_{depl}$  + $C_{inv}$  or  $C_{acc}$ ) and interface trap capacitance,  $C_{it}$ . Proper  $C_{it}$  extraction is dependent on the accuracy of  $C_s$  vs.  $\Phi_s$  curve. Semiconductor surface potential,  $\Phi_s$  can be extracted from gate C-V according to the following equation using Berglund integral [14]:

$$\phi_s = \int_{V_{FB}}^{V_g} \left( 1 - \frac{C(V_g)}{C_{ox}} \right) dV_g$$

(7)

Here  $V_{FB}$  is the flat-band voltage. We can get trap charge,  $Q_{it}$  by integrating  $C_{it}$  using the following equation.

$$Q_{it} = \int_{0}^{\phi_s} C_{it} d\phi_s + q \tag{8}$$

Here q is a constant of integration. The density of states,  $D_{it}$  and  $Q_{it}$  are related through the Fermi-Dirac occupation probability by the following relation.

$$Q_{it} = -q \int_{E_i}^{\infty} F(E) D_{it} dE + q \int_{-\infty}^{E_i} \left[ 1 - F(E) \right] D_{it} dE \qquad (9)$$

For simplicity, a step-like Fermi-Dirac function is assumed in  $D_{it}$  extraction. This assumption reduces the relation between  $Q_{it}$  and  $D_{it}$  to the following equation:

$$D_{it}(E) = \frac{1}{q} \times \left| \frac{dQ_{it}(E)}{dE} \right|$$

(10)

# IV. RESULTS

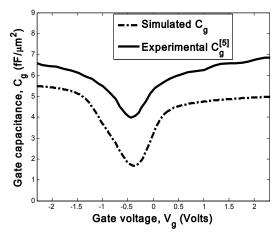

Fig. 2. shows the experimental [5] and simulated low frequency gate capacitance versus voltage curves for  $Al_2O_3/In_{0.75}Ga_{0.25}As$  /  $In_{0.53}Ga_{0.47}As$  MOSFET. The extracted  $C_p$

Fig. 2. Simulated and experimental [5] gate capacitance versus gate voltage for  $Al_2O_3/In_{0.75}Ga_{0.25}As/In_{0.53}Ga_{0.47}As$  MOSFET ( $t_{ox}$ = 10 nm).

and simulated  $C_s$  vs.  $\Phi_s$  are also presented in Fig. 3. The difference between two curves represents interface trap capacitance,  $C_{it}$ . It is noted from Figure 2 and 3 that experimental and ideal gate capacitances or semiconductor capacitances do not merge at strong accumulation and inversion bias unlike conventional Si MOS structures. It may be attributed to the fact that  $D_{it}$  profile exists outside the bandgap for III-V/high- $\kappa$  interface resulting in nonzero  $C_{it}$  outside the bandgap.

Fig. 3: Parallel and semiconductor capacitance versus surface potential for  $Al_2O_3/In_{0.75}Ga_{0.25}As/In_{0.53}Ga_{0.47}As$  MOSFET.

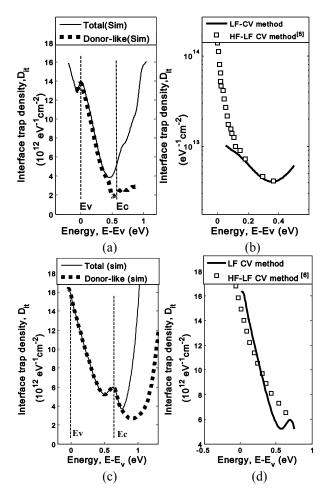

Fig. 4(a) and (c) shows the extracted D<sub>it</sub> along with donor-like trap profile while Fig. 4(b) and (d) shows a comparison of our simulated D<sub>it</sub> profile with the reported D<sub>it</sub> profile measured by HF-LF CV technique [5], [6] for  $In_{0.75}Ga_{0.25}As$ - and In<sub>0.65</sub>Ga<sub>0.35</sub>As-channel MOSFETs respectively. It is evident from the figure that the simulation results are in good agreement in weak accumulation and depletion bias but disagreement remains in strong accumulation and strong inversion when Fermi level at the surface crosses the valence or conduction band edges. This deviation is due to the fact that the combined HF-LF CV technique is based essentially on semiclassical physics which gives accurate results only within the bandgap, away from the band edges [13]. Close inspection reveals difference between the two profiles even within the band gap. This is more pronounced at the onset of inversion. The combined HF-LF CV technique is accountable for this discrepancy because the minority carriers cannot respond fast enough to follow the high frequency inversion bias [13]. This disagreement is more prominent in low-bandgap materials like In<sub>0.75</sub>Ga<sub>0.25</sub>As with high minority carrier concentration ( $\sim 10^{14}$  cm<sup>-3</sup>). A comparison between the simulated data (LF CV method) and measured data (HF-LF CV method) [5], [6] for both  $Al_2O_3/In_{0.65}Ga_{0.35}As/$ In<sub>0.53</sub>Ga<sub>0.47</sub>As and Al<sub>2</sub>O<sub>3</sub>/ In<sub>0.75</sub>Ga<sub>0.25</sub>As/ In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET is presented in table II.

Fig. 4. Interface traps density vs. energy for (a)  $Al_2O_3$ /  $In_{0.75}Ga_{0.25}As$  /  $In_{0.53}Ga_{0.47}As$  MOSFET (c)  $Al_2O_3$ /  $In_{0.65}Ga_{0.35}As$  /  $In_{0.53}Ga_{0.47}As$  MOSFET. Extracted Dit profile (LF CV method) and reported Dit profile (HF-LF CV method) for (b)  $Al_2O_3$ /  $In_{0.75}Ga_{0.25}As$  /  $In_{0.53}Ga_{0.47}As$  MOSFET [5] and (d)  $Al_2O_3$ /  $In_{0.65}Ga_{0.35}As$  /  $In_{0.53}Ga_{0.47}As$  MOSFET [6]. In both cases  $t_{ox}$ = 10nm, Na= 1×10<sup>17</sup> cm<sup>-3</sup>.

It is observed that increasing In-content from 65% to 75% decreases the interface trap density. This decreasing phenomenon may be explained by the reduction of the density of the  $Ga^{3+}$  oxidation state with increasing In concentration, as the gallium concentration is concomitantly reduced which leads to smaller number of defect states at the

| TABLE II<br>Comparison of Dit Profiles |                                                     |                          |                                          |                |                          |      |  |  |

|----------------------------------------|-----------------------------------------------------|--------------------------|------------------------------------------|----------------|--------------------------|------|--|--|

|                                        | $D_{IT}(E)(10^{12} \text{ cm}^{-2} \text{eV}^{-1})$ |                          |                                          |                |                          |      |  |  |

| –<br>Method =                          | In <sub>0.65</sub> Ga <sub>0.35</sub> As            |                          | In <sub>0.75</sub> Ga <sub>0.25</sub> As |                |                          |      |  |  |

|                                        | E <sub>C</sub>                                      | E <sub>mid</sub><br>-gap | Ev                                       | E <sub>C</sub> | E <sub>MID</sub><br>-gap | Ev   |  |  |

| HF-LF<br>CV                            | 6.7                                                 | 8.4                      | 16                                       |                | 5                        | 140  |  |  |

| LF CV                                  | 5.6                                                 | 8.98                     | 16.3                                     | 4.87           | 6.14                     | 13.9 |  |  |

interface [15]. At the same time, percentage of donor-like traps increases in the  $D_{it}$  profile. This phenomenon is explained by the charge-neutrality-level model for III-V MOSFETs [16].

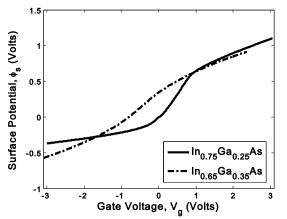

It is observed that charge neutrality level (CNL) moves closer to conduction band minimum (CBM) with increasing In-content. For  $In_{0.75}Ga_{0.25}As$ , the energy difference between CBM and CNL is only 0.06 ev. On the other hand, this quantity is higher (0.15 ev) for  $In_{0.65}Ga_{0.35}As$  [16]. As the quantity of interface- trapped positive charges (donor-like traps) dominate below CNL, donor-like traps dominate in both  $In_{0.75}Ga_{0.25}As$  and  $In_{0.65}Ga_{0.35}As$ -channel devices while the quantity is higher for the former. This large number of donor-like interface states aid in attaining stronger inversion by contributing carriers in the channel layer of the nMOSFET. As a result, the amount of band bending or surface potential movement reasonably increases from  $In_{0.65}Ga_{0.35}As$  to  $In_{0.75}Ga_{0.25}As$ -channel devices.

Fig. 5. Surface potential versus gate voltage for both  $In_{0.65}Ga_{0.35}As$ and  $In_{0.75}Ga_{0.25}As$ -channel MOSFETs. In both cases  $t_{ox}$ = 10nm,  $N_a$ =  $1 \times 10^{17}$  cm<sup>-3</sup>.

Fig. 5 presents a comparison of the movement of surface potential with variation of gate voltage for these two channel materials. In both cases, band bends considerably at the interface to meet the requirement of strong inversion. However, at depletion and weak inversion region, the slope or variation is higher for  $In_{0.75}Ga_{0.25}As$ -channel MOSFETs as expected.

This result is in agreement with the transport characteristics showed by Y. Xuan et. al [5]. It is observed that maximum drain current increases from 0.86A/mm to 1.0 A/mm for increasing In-content of the channel from 65% to 75% at a gate bias of 4.0 volt.

# V. CONCLUSION

A complete characterization of  $D_{it}$  profile of the InGaAs heterostructure MOSFET is performed. It reveals a very important fact that majority of the traps are donor-like. So, the device exhibits strong inversion characteristics in spite

of high interface trap density of high-  $\kappa$ /III-V interface. This result is consistent with the findings reported by Varghese et al. [6]. However, this dominant donor-like interface property is found only in those III-V materials which have charge neutrality level lying in the upper half of the bandgap.

### ACKNOWLEDGMENT

The authors acknowledge the support from the department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology in carrying out this research.

#### REFERENCES

- [1] International Technology Roadmap for Semiconductors (2009 Edition), Executive Summary.

- Available: http://www.itrs.net/Links/2009ITRS/Home2009.htm

- [2] Y. Xuan, Y.Q. Wu, H.C. Lin, T. Shen, and P. D. Ye, "Submicrometer inversion-type enhancement-mode InGaAs MOSFET with atomiclayer-deposited Al<sub>2</sub>O<sub>3</sub> as gate dielectric,"*IEEE Electron Devices Letters*, vol. 28, no. 11, pp. 935 – 938, November 2007.

- [3] Y. Xuan, Y.Q. Wu, T. Shen, T. Yang and P. D. Ye, "High performance submicron inversion-type enhancement-mode InGaAs MOSFETs with ALD Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, and HfAlO as gate dielectrics" in *IEEE IEDM tech digest*, 2008, pp. 637-640.

- [4] Y. Xuan, Y. Q. Wu, and P. D. Ye, "High-performance inversion-type enhancement-mode InGaAs MOSFET with maximum drain current exceeding 1 A/mm," *IEEE Electron Devices Letters*, vol. 29, no. 4, pp. 294 – 296, April 2008.

- [5] Y. Xuan, T. Shen, M. Xu, Y.Q. Wu and P.D. Ye, "High-performance surface channel In-rich In<sub>0.75</sub>Ga<sub>0.25</sub>As MOSFETs with ALD high-k as gate dielectric," in *IEEE IEDM tech digest*, 2008, pp. 371-374.

- [6] D. Varghese, Y. Xuan, Y. Q. Wu, T. Shen, P. D. Ye, and M. A. Alam, "Multiprobe interface characterization of In<sub>0.65</sub>Ga<sub>0.35</sub>As/Al<sub>2</sub>O<sub>3</sub> MOSFET," in *IEEE IEDM tech digest*, 2008, pp. 379-382.

- [7] Y. Q. Wu, M. Xu, R.S. Wang, O. Koybasi and P. D. Ye, "High performance deep-submicron inversion-mode InGaAs MOSFETs with maximum Gm exceeding 1.1 mS/um: new HBr pretreatment and channel engineering," in *IEEE IEDM tech digest*, 2009, pp. 323-326.

- [8] F. Stern, "Self-consistent results for n-type Si inversion layers," *Phys. Rev. B*, vol. 5, pp. 4891–4899, 1972.

- [9] Supriyo Datta, *Quantum Transport: Atom to Transistor*, Cambridge University, 1<sup>st</sup> Ed., 2005.

- [10] A. E. Islam and A. Haque, "Accumulation gate capacitance of MOS devices with ultrathin high-κ gate dielectrics: modeling and characterization," *IEEE Transactions on Electron Devices*, vol. 53, no. 6, pp. 1364–1372, June 2006.

- [11] J. Piprek, Semiconductor Optoelectronic Devices: Introduction to Physics and Simulation, San Diego (CA): Academic Press, 2003.

- [12] M. M. Satter and A. Haque, "Direct extraction of interface trap states from the low frequency gate C-V characteristics of MOS devices with ultrathin high-κ gate dielectrics," in *ICECE*, 2008.

- [13] M. M. Satter and A. Haque, "Modeling effects of interface traps on the gate C-V characteristics of MOS devices on alternative high-mobility substrate," *Solid-State Electronics*, vol. 54, no. 6, pp. 621-627, 2010.

- [14] C. N. Berglund, "Surface states at steam-grown silicon-silicon dioxide interfaces," *IEEE Transactions On Electron Devices*, vol.-13, no. 10, October 1966.

- [15] Serge Oktyabrsky, Piede D. Ye, Ed., Fundamentals of III-V Semiconductor MOSFETs, 1<sup>st</sup> ed., Springer, 2010, pp. 163-165.

- [16] Peide. D. Ye, "Main determinants for III-V metal-oxidesemiconductor field-effect transistors," *Journal of Vacuum Science Technology*, vol. 26, no. 4, Jul/Aug 2008.